FPGA Mastermind Game

Fall 2018

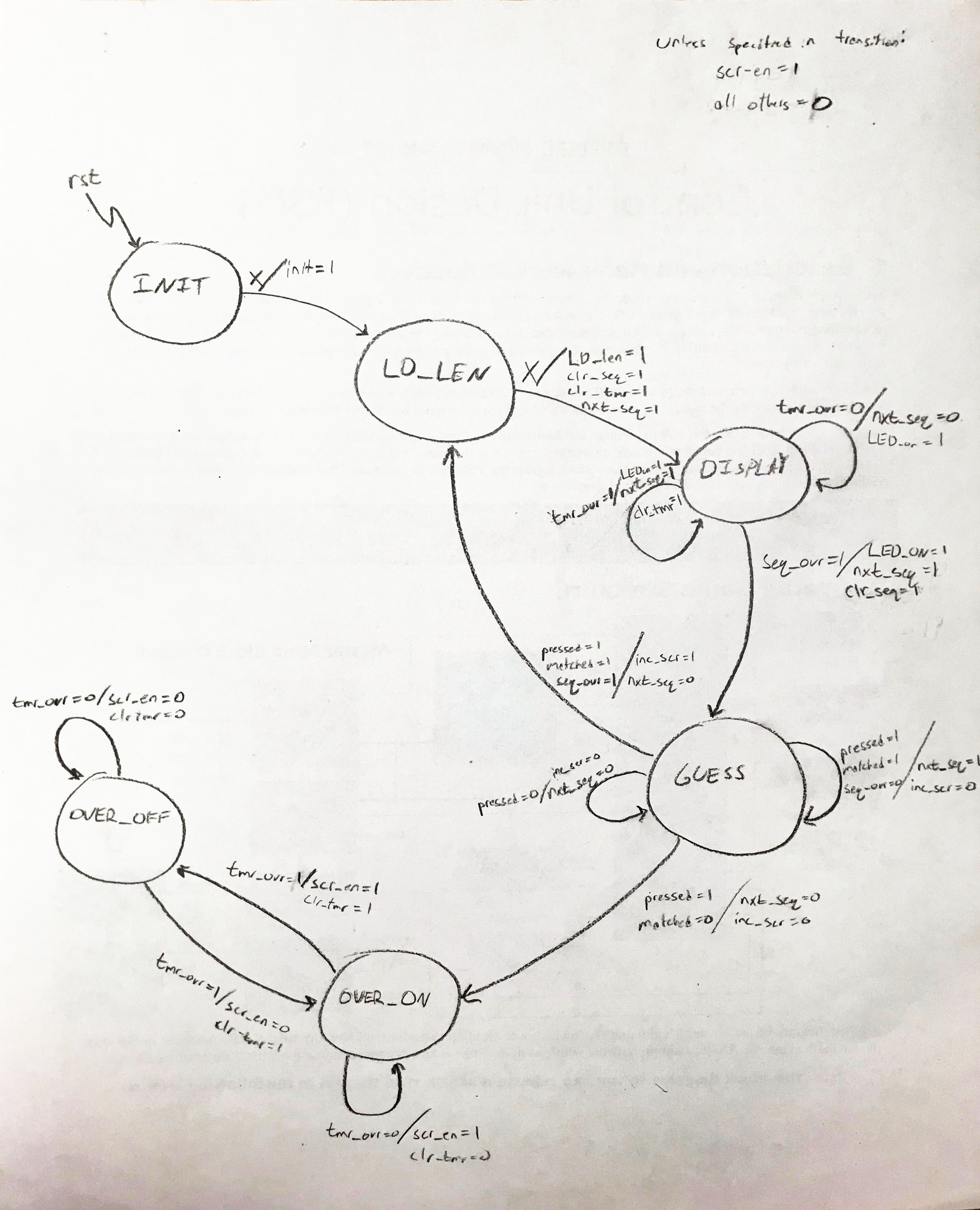

Mastermind is a puzzel/memory game where the player is shown a pattern on a set of four LEDs and then must reproduce that pattern by pressing the four buttons in the correct order. This version of Mastermind was implemented entirely on FPGA hardware using a one-hot state machine built in Quartus. We first designed our state machine on paper, making note of all of the input/output values associated with each state transition.

Figure 1: The state diagram

We then went about designing our state machine. Each flip-flop represents one state of the state machine, and each one has an input that determines what state the machine will go to next. We used k-maps to determine the logic for each of these next state bits. What we're left with is then a simple boolean expression for each bit that we can build out of basic digital gates.

Figure 2: The state machine

Next we implemented the logic in Quartus. We mapped each button as an input and the LEDs as an output on the FPGA board. We also imported a file containing all the game patterns and used a verilog file to manage the retrieval of these game patterns from memory.

The last step was to upload the FPGA board in lab. Upon testing, our state machine successfully implemented the mastermind game, and it was pretty fun to play around with and see the state machine working.